### Summary

Tutorial TU0117 (v1.5) October 31, 2006 This introductory tutorial is designed to give you an overview of how to create a schematic, update the design information to a PCB and generate manufacturing output files. It also investigates the concept of projects and integrated libraries.

Welcome to the world of Altium Designer – a complete electronic product development environment. This tutorial will get you started with creating a PCB project based on an astable multivibrator design.

If you are new to Altium Designer then you might like read the guide *Welcome to the Altium Designer Environment* for an explanation of the interface, information on how to use panels and managing design documents.

### **Creating a new PCB project**

A project in Altium Designer consists of links to all documents and setups related to a design. A project file, e.g. xxx.PrjPCB, is an ASCII text file that lists which documents are in the project and related output setups, e.g. for printing and CAM. Documents that are not associated with a project are called 'free documents'. Links to schematic sheets and a target output, e.g. PCB, FPGA, embedded (VHDL) or library package, are added to a project. Once the project is compiled, design verification, synchronization and comparison can take place. Any changes to the original schematics or PCB, for example, are updated in the project when compiled.

The process of creating a new project is the same for all project types. We will use the PCB project as an example. We will create the project file first and then create the blank schematic sheet to add the new empty project. Later in this tutorial we will create a blank PCB and add it to the project as well.

To start the tutorial, create a new PCB project:

Select File » New » Project » PCB Project from the menus, or click on Blank Project (PCB) in the New section of the Files panel. If this panel is not displayed, click on the Files tab at the bottom of the Design Manager panel.

Alternatively, you could select **Printed Circuit Board Design** in the Pick a Task section of the Altium Designer Home Page (**View** » Home) and then click on **New Blank PCB Project**.

2. The **Projects** panel displays. The new project file, PCB\_Project1.PrjPCB, is listed here with no documents added.

| P | rojects                        |   | 🔻 🖉 🗙     |

|---|--------------------------------|---|-----------|

|   | Workspace1.DsnWrk              | • | Workspace |

|   | PCB_Project1.PrjPCB            |   | Project   |

|   | ● File View ○ Structure Editor |   | •ف ک      |

|   | E PCB_Project1.PrjPCB          |   |           |

|   | No Documents Added             |   |           |

3. Rename the new project file (with a .PrjPCB extension) by selecting File » Save Project As. Navigate to a location where you would like to store the project on your hard disk, type the name Multivibrator.PrjPCB in the File Name field and click on Save.

Next we will create a schematic to add to the empty project file. This schematic will be for an astable multivibrator circuit.

### Creating a new schematic sheet

Create a new schematic sheet by completing the following steps:

1. Select File » New » Schematic, or click on Schematic Sheet in the New section of the Files panel. A blank schematic sheet named Sheet1.SchDoc displays in the design window and the schematic document is automatically added (linked) to the project. The schematic sheet is now listed under Source Documents beneath the project name in the Projects tab.

Rename the new schematic file (with a .SchDoc extension) by selecting File » Save As. Navigate to a location where you would like to store the schematic on your hard disk, type the name Multivibrator.SchDoc in the File Name field and click on Save.

When the blank schematic sheet opens you will notice that the workspace changes. The main toolbar includes a range of new buttons, new toolbars are visible, the menu bar includes new items and the **Sheet** panel is displayed. You are now in the Schematic Editor.

You can customize many aspects of the workspace. For example, you can reposition the panels and toolbars or customize the menu and toolbar commands.

Now we can add our blank schematic to the project before proceeding with the design capture.

### Adding schematic sheets to a project

If the schematic sheets you want to add to a project file have been opened as Free Documents, rightclick on the project name in the Projects panel and select **Add Existing to Project**. Choose the free documents name(s) and click **Open**. Alternatively, you could drag-and-drop the free document into the project documents list in the Projects panel. The schematic sheet is now listed under Source Documents beneath the project name in the Projects tab and is linked to the project file.

## Setting the schematic options

The first thing to do before you start drawing your circuit is to set up the appropriate document options. Complete the following steps.

- From the menus, choose Design » Document Options and the Document Options dialog will open. For this tutorial, the only change we need to make here is to set the sheet size to standard A4 format. In the Sheet Options tab, find the Standard Styles field. Click the arrow next to the entry to see a list of sheet styles.

- 2. Select the **A4** style and click the **OK** button to close the dialog and update the sheet size.

- 3. To make the document fill the viewing area again, select **View** » **Fit Document**.

In Altium Designer, you can activate any menu by simply pressing the menu hotkey (the underlined letter in the menu name). Any subsequent menu items will also have hot keys that you can use to activate the item. For example, the shortcut for selecting the **View** » **Fit Document** menu item is to press the **V** key followed by the **D** key. Many submenus, such as the **Edit** » **DeSelect** menu, can be called directly. To activate the **Edit** » **DeSelect** » **All on Current Document** menu item, you need only press the **X** key (to call up the DeSelect menu directly) followed by the **A** key.

Next we will set the general schematic preferences.

- Select Tools » Schematic Preferences [shortcut T, P] to open the schematic Preferences dialog. This dialog allows you to set global preferences that will apply to all schematic sheets you work on.

- Click on Schematic Default Primitives in the selection tree (left side of the dialog) to make it the active page and enable the Permanent check box. Click the OK button to close the dialog.

- Before you start capturing your schematic, save this schematic sheet, so select File » Save [shortcut F, S].

Altium Designer has a multilevel Undo, allowing you to undo any number of previous actions. The maximum number of Undo steps is userconfigurable and limited only by the available memory on your computer.

You can save any schematic sheet as a document template (.schdot) allowing you to include special information such as a custom company title block and logo.

## **Drawing the schematic**

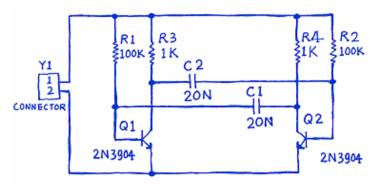

You are now ready to begin capturing (drawing) the schematic. For this tutorial, we will use the circuit shown below (Figure 1). This circuit uses two 2N3904 transistors configured as a self-running astable multivibrator.

Figure 1. An astable multivibrator

### Locating the component and loading the libraries

To manage the thousands of schematic symbols included with Altium Designer, the Schematic Editor provides powerful library search features. Although the components we require are in the default installed libraries, it is useful to know how to search through the libraries to find components. Work through the following steps to locate and add the libraries you will need for the tutorial circuit.

First we will search for the transistors, both of which are type 2N3904.

- 1. Click on the **Libraries** tab to display the **Libraries** panel.

- Press the Search button in the Libraries panel, or select Tools » Find Component, to open the Libraries Search dialog.

- 3. Ensure that the Scope is set to Libraries on Path and that the Path field contains the correct path to your libraries. If you accepted the default directories during installation, the path should be C:\Program Files\Altium

| Libraries Sear                   | ch         |            | ?                                    | × |

|----------------------------------|------------|------------|--------------------------------------|---|

| *3904*                           |            |            |                                      |   |

| Options                          |            |            |                                      |   |

| Search type                      | Components |            | ▼                                    |   |

| 🔽 Clear existir                  | ng query   |            |                                      |   |

| Scope                            |            | Path       |                                      |   |

| 🔿 Available lit                  | oraries    | Path:      | M FILES\ALTIUM DESIGNER 6\Library\ 😝 |   |

| <ul> <li>Libraries or</li> </ul> | path       |            | Include Subdirectories               |   |

| O Refine last                    | search     | File Mask: | × × .                                |   |

| <u> </u>                         | 🗙 Clear 🛛  | Helper     | History Favorites Cancel             |   |

Designer 6\Library\. Click on the folder icon to browse to the library folder. Ensure that the **Include Subdirectories** box is not selected (not ticked) for this example.

4. We want to search for all references to 3904, so type \*3904\* in the query section at the top of the *Libraries Search* dialog. The \* symbol is a wildcard used to take into account the different prefixes and suffixes used by different manufacturers.

- 5. Click the **Search** button to begin the search. The Query Results are displayed in the **Libraries** panel as the search takes place.

- Click on the component name 2N3904 found in the Miscellaneous Devices.IntLib library to select it. This library has symbols for all the available simulationready BJT transistors.

- 7. If you choose a component that resided in a library that was not currently installed, you would be asked to confirm the installation of that library before you could place the component on your schematic. Since the Miscellaneous Devices library we need is already installed by default, the component is ready to place.

The added libraries will appear in the drop down list at the top of the Libraries panel. As you click on a library name in the upper list, the components in that library are listed below. The component filter in the panel can then be used to quickly locate a component within a library.

### Placing the components on your schematic

The first components we will place on the schematic are the two transistors, Q1 and Q2. For the general layout of the circuit, refer to the schematic drawing shown in Figure 1.

- 1. Select View » Fit Document [shortcut V, D] to ensure your schematic sheet takes up the full window.

- 2. Make sure the Libraries panel is displayed by clicking on the Libraries tab.

- 3. Q1 and Q2 are BJT transistors, so select the Miscellaneous Devices.IntLib library from the Libraries drop-down list at the top of the Libraries panel to make it the active library.

- 4. Use the filter to quickly locate the component you need. The default wildcard (\*) will list all components found in the library. Set the filter by typing \*3904\* in the filter field below the Library name. A list of components which have the text "3904" as part of their Component Name field will be displayed.

- 5. Click on the 2N3904 entry in the list to select it, then click the Place button. Alternatively, just double-click on the component name. The cursor will change to a cross hair and you will have an outlined version of the transistor "floating" on your cursor. You are now in part placement mode. If you move the cursor around, the transistor outline will move with it.

- Before placing the part on the schematic, first edit its properties. While the transistor is floating on the cursor, press the **TAB** key. This opens the *Component Properties* dialog for the component. We will now set up the dialog options to appear as below.

| Libraries     |                                   | <b>▼</b> ×                        |

|---------------|-----------------------------------|-----------------------------------|

| Libraries     | Search                            | Place 2N3904                      |

| Miscellaneous | Devices.IntLib                    | ¥                                 |

| *3904*        |                                   | ~                                 |

| Comp 🛆 D      |                                   | y Footprint<br>Ilaneous BCY-W3/E4 |

|               |                                   |                                   |

| 196 componer  | nts                               |                                   |

|               | Q?<br>2N39                        | 104                               |

|               | <u> </u>                          |                                   |

| Model Name    | Type 🛆                            | Source                            |

| 2N3904        | 3/E Footprint<br>Signal Integrity | Miscellaneous Device              |

| m 2N3904      |                                   | 2N3904.mdl                        |

|               |                                   |                                   |

|               |                                   | ~                                 |

|               |                                   | 3                                 |

|               |                                   | 1                                 |

|               |                                   | L                                 |

|               |                                   |                                   |

| roperties –                                                                 |                                                   |        |                          | P                                                    | arameters for Q? • 2N3904                            |                  |

|-----------------------------------------------------------------------------|---------------------------------------------------|--------|--------------------------|------------------------------------------------------|------------------------------------------------------|------------------|

| Designator                                                                  | Q? Visible                                        | Locked | Visible                  | Name                                                 | / Value                                              | Туре             |

| Comment                                                                     | 2N3904 Visible                                    |        |                          | Code_JEDEC                                           | TO-92A                                               | STRING           |

| omment                                                                      |                                                   | _      |                          | DatasheetDocument                                    | 1997                                                 | STRING           |

|                                                                             | Contraction Part 1/1                              | Locked |                          | LatestRevisionDate                                   | 15Jan-2003                                           | STRING           |

| ibrary Ref                                                                  | 2N3904                                            |        |                          | LatestRevisionNote                                   | PCB Footprint 'BCY-W3/D4.7' replace                  |                  |

|                                                                             | Miscellaneous Devices IntLib                      |        |                          | PackageReference                                     | T0-92A                                               | STRING           |

| .ibrary                                                                     | Miscellaneous Devices.IntLib                      |        |                          | Published                                            | 8-Jun-2000                                           | STRING           |

| escription                                                                  | NPN General Purpose Amplifier                     |        |                          | Publisher                                            | Altium Limited                                       | STRING           |

| Jnique Id                                                                   | WEMGYXLD                                          | Reset  |                          |                                                      |                                                      |                  |

| уре                                                                         | Standard                                          | ~      |                          |                                                      |                                                      |                  |

|                                                                             | 5                                                 |        |                          |                                                      |                                                      |                  |

| ub-Design L                                                                 | inks                                              |        |                          |                                                      |                                                      |                  |

| ub-Design L<br>ub-Project                                                   |                                                   |        |                          |                                                      |                                                      |                  |

| ub-Project                                                                  | None                                              |        | Add                      | Remo <u>v</u> e                                      | <u>E</u> dit Add as <u>R</u> ule                     |                  |

| ub-Project                                                                  | None                                              |        | <u>A</u> dd              |                                                      | Edit Add as <u>B</u> ule                             |                  |

| ub-Project<br>onfiguration<br>raphical                                      | None None                                         |        | Add                      |                                                      |                                                      |                  |

| ub-Project<br>onfiguration<br>raphical<br>.ocation X                        | None<br>None<br>740 Y 530                         |        | Name<br>2N3904           | Type<br>Simulation                                   | Models for Q? - 2N3904<br>C Description<br>NPN       |                  |

| ub-Project<br>onfiguration<br>raphical —<br>.ocation X<br>Drientation       | None<br>None<br>740 Y 530<br>0 Degrees Y Mirrored |        | Name<br>2N3904<br>2N3904 | Type<br>Simulation<br>Signal Integr                  | Models for Q? - 2N3904<br>C Description<br>NPN<br>ty |                  |

| ub-Project<br>onfiguration<br>raphical<br>.ocation X<br>Drientation<br>Mode | None<br>None<br>740 Y 530<br>0 Degrees V Mirrored |        | Name<br>2N3904           | Type<br>Simulation<br>Signal Integr                  | Models for Q? - 2N3904<br>C Description<br>NPN       | ds; Body Dia. 4. |

| ub-Project<br>onfiguration<br>raphical<br>.ocation X<br>Drientation<br>Mode | None<br>None<br>740 Y 530<br>0 Degrees Y Mirrored |        | Name<br>2N3904<br>2N3904 | Type<br>Simulation<br>Signal Integr<br>4 ▼ Footprint | Models for Q? - 2N3904<br>C Description<br>NPN<br>ty | ds; Body Dia. 4. |

- 7. In the **Properties** section of the dialog, set the value for the first component designator by typing Q1 in the **Designator** field.

- 8. Next we will check the footprint that will be used to represent the component in the PCB. For this tutorial, we have used integrated libraries which mean that the recommended models for footprints and circuit simulation are already included. Make sure that footprint name BCY-W3/E4 is included in the Models list. Leave all other fields at their default values and click **OK** to close the dialog.

You are now ready to place the part.

- Move the cursor (with the transistor symbol attached) to position the transistor a little left of the middle of the sheet. Once you are happy with the transistor's position, left-click or press ENTER to place the transistor onto the schematic.

- 2. Move the cursor and you will find that a copy of the transistor has been placed on the schematic sheet, but you are still in part placement mode with the part outline floating on the cursor. This feature of Altium Designer allows you to place multiple parts of the same type. So let's now place the second transistor. This transistor is the same as the previous one, so there is no need to edit its attributes before we place it. Altium Designer will automatically increment a component's designator when you place a series of parts. In this case, the next transistor we place will automatically be designated Q2.

- 3. If you refer to the schematic diagram (Figure 1) you will notice that Q2

The link between the schematic component and the PCB component is the footprint. The footprint specified in the schematic is loaded from the PCB library when you load the netlist. Double-click on a schematic component to specify the footprint.

When you are in any editing or placement mode (a cross hair cursor is active), moving the cursor to the edge of the document window will automatically pan the document.

If you accidentally pan too far while you are wiring up your circuit, press V, F (View » Fit All Objects) to redraw the schematic window, showing all placed objects. This can be done even when you are in the middle of placing an object.

is drawn as a mirror of Q1. To flip the orientation of the transistor that is floating on the cursor, press the X key. This flips the component horizontally.

- Move the cursor to position the part to the right of Q1. To position the component more accurately, press the **PAGEUP** key twice to zoom in two steps. You should now be able to see the grid lines.

- Once you have positioned the part, left-click or press ENTER to place

Q2. Once again a copy of the transistor you are "holding" will be placed on the schematic, and the next transistor will be floating on the cursor ready to be placed.

- 6. Since we have now placed all the transistors, we will exit part placement mode by clicking the right mouse button or pressing the **ESC** key. The cursor will revert back to a standard arrow.

Next we will place the four resistors.

- 1. In the Libraries panel, make sure the Miscellaneous Devices.IntLib library is active.

- 2. Set the filter by typing res1 in the filter field below the Library name.

- 3. Click on **Res1** in the components list to select it, then click the **Place** button. You will now have a resistor symbol floating on the cursor.

- 4. Press the **TAB** key to edit the resistor's attributes. In the Properties section of the dialog, set the value for the first component designator by typing R1 in the Designator field.

- 5. Make sure that footprint name AXIAL-0.3 is included in the Models list.

- The contents of Comment field of the schematic component maps to the Comment field of the PCB component, typically you would enter the value or the resistor here. Enter a value of 100k into the Comment field for R1.

Components being simulated may have a number of simulation properties that can be defined (eg, a resistor has 1, a BJT has 5, and a MOSFET has 13), these properties are defined by using Parameters. If you wanted to simulate this circuit then the resistor value must be defined as a Parameter, whose name is Value and whose value is the resistance.

If the circuit being captured is for both simulation and PCB layout, rather than enter the value twice (in the parameter called Value and then in the Comment field), Altium Designer supports 'indirection', a feature that maps any parameter's string into the Comment field. If you click to display the Comment field dropdown list you will see that the software has automatically build a list of all current parameters, in case you want to map the value of one of them into the Comment field.

- 7. Since you will not be simulating ensure that the Visible check box for the Value parameter is clear.

- 8. Press the **SPACEBAR** to rotate the resistor by 90° so it is in the correct orientation.

- Position the resistor above the base of Q1 (refer to the schematic diagram in Figure 1) and left-click or press ENTER to place the part. Don't worry about making the resistor connect to the transistor just yet. We will wire up all the parts later.

- 10. Next place the other 100k resistor R2 above the base of Q2. The designator will automatically increment when you place the second resistor.

- 11. The remaining two resistors, R3 and R4, have a value of 1k, so press the **TAB** key to call up the *Component Properties* dialog, enter 1k into the **Comment**, and confirm that the **Visible** checkbox for the **Value** parameter is cleared. Click **OK** to close the dialog.

Use the following keys to manipulate the part floating on the cursor:

- Y flips the part vertically

- X flips the part horizontally

- Spacebar rotates the part by 90°.

#### To edit the attributes of an object placed on the schematic, double-click the object to open its *Component Properties* dialog.

12. Position and place R3 and R4 as shown in the schematic diagram in Figure 1. Right-click or press **ESC** to exit part placement mode.

Now place the two capacitors.

- 1. The capacitor part is also in the Miscellaneous Devices.IntLib library, which should already be selected in the **Libraries** panel.

- 2. Type cap in the component's filter field in the Libraries panel.

- 3. Click on **CAP** in the components list to select it, then click the **Place** button. You will now have a capacitor symbol floating on the cursor.

- 4. Press the **TAB** key to edit the capacitor's attributes. In the *Component* Properties dialog set the **Designator** to C1, the **Comment** to 20n, clear the **Visible** checkbox for the **Value** parameter, and check the PCB footprint model RAD-0.3 is selected in the **Models** list. Click **OK**.

As with the resistor, if you wanted to simulate this circuit you would need a Value parameter with the value of 20n, in this case you would define the capacitance in the Value parameter and then use the indirection feature to map the contents of the value parameter into the Comment field. Since you will not be simulating ensure that the **Visible** check box for the **Value** parameter is clear.

- 5. Position and place the two capacitors in the same way that you placed the previous parts.

- 6. Right-click or press **ESC** to exit placement mode.

The last component to be placed is the connector, located in Miscellaneous Connectors.IntLib.

- 1. Select Miscellaneous Connectors.IntLib from the Libraries list in the Libraries panel. The connector we want is a two-pin socket, so set the filter to \*2\*.

- Select Header 2 from the parts list and click the Place button. Press TAB to edit the attributes and set Designator to Y1 and check the PCB footprint model is HDR1X2. No Value parameter is required as you would replace this component with a power source when simulating the circuit. Click OK to close the dialog.

- 3. Before placing the connector, press **X** to flip it horizontally so that it is in the correct orientation. Click to place the connector on the schematic.

- 4. Right-click or press **ESC** to exit part placement mode.

- 5. Save your schematic by selecting File » Save from the menus [shortcut F, S].

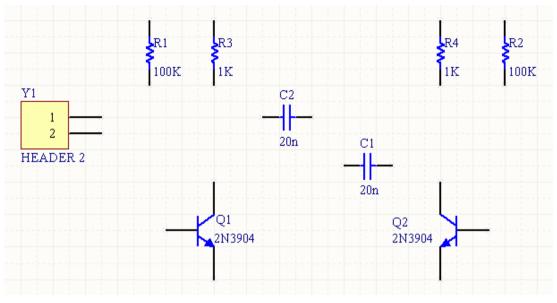

You have now placed all the components. Note that the components in Figure 2 are spaced so that there is plenty of room to wire to each component pin. This is important because you can not place a wire across the bottom of a pin to get to a pin beyond it. If you do, both pins will connect to the wire.

If you need to move a component, click-and-hold on the body of the component, then drag the mouse to reposition it.

To reposition any object, simply place the cursor directly over the object, click-and-hold the left mouse button, drag the object to a new position and then release the mouse button.

Figure 2. Schematic with all parts placed.

### Wiring up the circuit

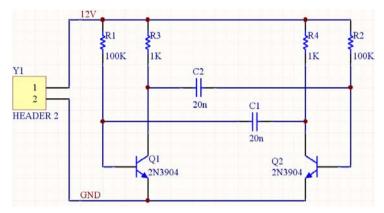

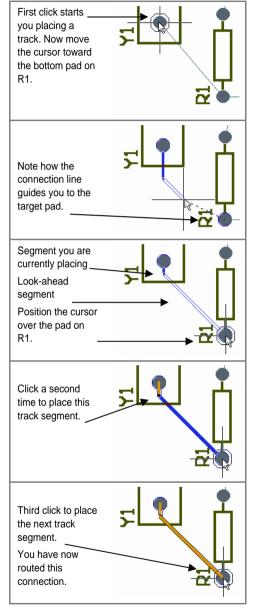

Wiring is the process of creating connectivity between the various components of your circuit. To wire up your schematic, refer to the diagram in Figure 1 and complete the following steps.

- To make sure you have a good view of the schematic sheet, use the PAGE UP key to zoom in or PAGE DOWN to zoom out. Also try holding down the **Ctrl** key and using the mouse wheel to zoom.

- Firstly wire the resistor R1 to the base of transistor Q1 in the following manner. Select Place » Wire [shortcut P, W] from the menus or click on the Wire tool from the Wiring toolbar to enter the wire placement mode. The cursor will change to a crosshair.

- 3. Position the cursor over the bottom end of R1. When you are in the right position, a red connection marker (large asterisk) will appear at the cursor location. This indicates that the cursor is over an electrical connection point on the component.

- 4. Left-click or press **ENTER** to anchor the first wire point. Move the cursor and you will see a wire extend from the cursor position back to the anchor point.

- Position the cursor so that it is below R1 and level with the base of Q1. Left-click or press ENTER to anchor the wire at this point. The wire between the first and second anchor points will be placed.

- Position the cursor over the base of Q1 until you see the cursor change to a red connection marker. Left-click or press ENTER to connect the wire to the base of Q1.

- Note that the cursor remains a cross hair, indicating that you are ready to place another wire. To exit placement mode completely and go back to the arrow cursor, you would right-click or press ESC again – but don't do this just now.

To graphically edit the shape of a wire, or any other graphical object once it has been placed, position the arrow cursor over it and click once.

Whenever a wire runs across the connection point of a component, or is terminated on another wire, Altium Designer will automatically create a junction.

When placing wires, keep in mind the following points:

- left-click or press ENTER to anchor the wire at the cursor position;

- press BACKSPACE to remove the last anchor point;

- after placing the last segment of a wire, right-click or press

ESC to end the wire placement. The cursor will remain as a cross hair and you can begin placing another wire.

- Right-click again or press **ESC** to exit wire placement mode.

- 8. We will now wire C1 to Q1 and R1. Position the cursor over the left connection point of C1 and left-click or press ENTER to start a new wire. Move the cursor horizontally till it is directly over the wire connecting the base of Q1 to R1. A connection marker will appear. Left-click or press ENTER to place the wire segment, then right-click or press ESC to indicate that you have finished placing the wire. Note how the two wires are automatically connected.

- 9. Wire up the rest of your circuit, as shown in Figure 3.

A wire that crosses the end of a pin will connect to that pin, even if you delete the junction. Check that your circuit looks like Figure 3 before proceeding.

Figure 3. The fully wired schematic

- 10. When you have finished placing all the wires, right-click or press **ESC** to exit placement mode. The cursor will revert to an arrow.

- 11. If you wish to move any placed components and drag any connected wires with it, hold down the **Ctrl** key while moving the component, or select **Move** » **Drag**.

#### Nets and net labels

Each set of component pins that you have connected to each other now form what is referred to as a *net*. For example, one net includes the base of Q1, one pin of R1 and one pin of C1.

To make it easy to identify important nets in the design, you can add *net labels*. To place net labels on the two power nets:

- 1. Select Place » Net Label [shortcut P, N]. A dotted box will appear floating on the cursor.

- 2. To edit the net label before it is placed, press the TAB key to display the Net Label dialog.

- 3. Type 12V in the **Net** field, then click **OK** to close the dialog.

- 4. Place the net label so that the bottom left of the net label touches the upper most wire on the schematic. The cursor will change to a red cross when the net label touches the wire. If the cross is light gray, it means you are trying to label a pin instead.

- 5. After placing the first net label you will still be in net label placement mode, so press the **TAB** key again to edit the second net label before placing it.

- 6. Type GND in the **Net** field, click **OK** to close the dialog and place the net label. Right-click or press ESC to exit net label placement mode.

- 7. Select File » Save [shortcut F, S] to save your circuit. Save the project as well.

Congratulations! You have just completed your first schematic capture using Altium Designer.

Before we turn the schematic into a circuit board, let's set up the project options.

# **Setting up Project Options**

The project options include the error checking parameters, a connectivity matrix, Class Generator, the Comparator setup, ECO generation, output paths and netlist options, Multi-Channel naming formats, Default Print setups, Search Paths and any project parameters you wish to specify. Altium Designer will use these setups when you compile the project.

When a project is compiled, comprehensive design and electrical rules are applied to verify the design. When all errors are resolved, the re-compiled schematic designs are loaded into the target document, e.g. a PCB document, by generated ECOs. The project Comparator allows you to find differences between source and target files and update (synchronize) in both directions.

All project-related operations, such as error checking, comparing documents and ECO generation, are set up in the *Options for Project* dialog (**Project** » **Project Options**).

Project outputs, such as assembly and fabrication outputs and reports can be set up from the File menu options. You can also set up job options in a Job Options file (**File** » **New** » **Output Job File**). See *Setting up the Project Outputs* for more information.

1. Select Project » Project Options. The Options for Project dialog displays:

| Error Reporting Connection Matrix Class Generation Comparator ECO Generation ( | Dptions Multi-Channel Default Prints Search Paths Parameter |

|--------------------------------------------------------------------------------|-------------------------------------------------------------|

| Violation Type Description                                                     | A Report Mode                                               |

| Violations Associated with Documents                                           |                                                             |

| Conflicting Constraints                                                        | 🚞 Error                                                     |

| Duplicate sheet numbers                                                        | 🧀 Warning                                                   |

| Duplicate Sheet Symbol Names                                                   | 🚞 Error                                                     |

| Missing child sheet for sheet symbol                                           | 🚞 Error                                                     |

| Missing Configuration Target                                                   | 🚞 Error                                                     |

| Missing sub-Project sheet for component                                        | 🧀 Warning                                                   |

| Multiple Configuration Targets                                                 | 🚞 Fatal Error                                               |

| Multiple Top-Level Documents                                                   | 🗀 Error                                                     |

| Port not linked to parent sheet symbol                                         | 🗀 Error                                                     |

| Sheet Entry not linked to child sheet                                          | 🗀 Error                                                     |

| Unique Identifiers Errors                                                      | 🗀 Warning                                                   |

| <ul> <li>Violations Associated with Nets</li> </ul>                            |                                                             |

| Adding hidden net to sheet                                                     | 🗀 Warning                                                   |

| Adding Items from hidden net to net                                            | 🗀 Warning                                                   |

| Auto-Assigned Ports To Device Pins                                             | 🗀 Warning                                                   |

| Duplicate Nets                                                                 | Error                                                       |

| Floating net labels                                                            | 🗀 Warning                                                   |

| Floating power objects                                                         | 🗀 Warning                                                   |

| Global Power-Object scope changes                                              | 🗀 Warning                                                   |

| Net Parameters with no name                                                    | 🗀 Warning                                                   |

| Net Parameters with no value                                                   | 🗀 Warning                                                   |

| Nets containing floating input pins                                            | Error                                                       |

| Nets containing multiple similar objects                                       | 🗀 Error                                                     |

| Nets with multiple names                                                       | 🗀 Warning 🗾 🔻                                               |

| Nets with no driving source                                                    | No Report                                                   |

| Nets with only one pin                                                         | Warning                                                     |

| Nets with possible connection problems                                         |                                                             |

| Object constants district const                                                | Fatal Error                                                 |

2. Set up any project-related options in this dialog. We will now make some changes to the Error Reporting, Connection Matrix and Comparator tabs.

### Checking the electrical properties of your schematic

Schematic diagrams in Altium Designer are more than just simple drawings – they contain electrical connectivity information about the circuit. You can use this connectivity awareness to verify your design. When you compile a project, Altium Designer checks for errors according to the rules set up in the **Error Reporting** and **Connection Matrix** tabs and any violations generated will display in the **Messages** panel.

### Setting up Error Reporting

The **Error Reporting** tab in the *Options for Project* dialog is used to set up design drafting checks. The Report Mode is the level of severity of a violation. If you wish to change a Report Mode, click on a Report Mode next to the violation you wish to change and choose the level of severity from the drop-down list. For this tutorial we will use the default settings.

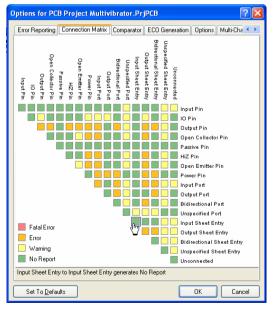

### Setting up the Connection Matrix

The **Connection Matrix** tab (*Options for Project* dialog) displays the severity of an error type that is produced when error reporting is run to check electrical connections within the design, i.e. connections between pins, ports and sheet entries. The matrix gives a graphical representation of different types of connection points on a schematic and whether they are allowable or not.

For example, look down the entries on the right side of the matrix diagram and find **Output Pin**. Read across this row of the matrix till you get to the **Open Collector Pin** column. The square where they intersect is orange indicating that an Output Pin connected to an Open Collector Pin on your schematic will generate an error condition when the project is compiled.

You can set each error type with a separate error level, e.g. from no report at all through to a fatal error. Right-click to see the menu options to control the entire matrix.

To make changes to the Connection Matrix:

- 1. Click on the **Connection Matrix** tab in the *Options for Project* dialog.

- 2. Click on the box that is at the intersection of two types of connection, e.g. Output Sheet Entry and Open Collector Pin.

- Click until the box changes to the color of the errors as listed in the legend, e.g. an orange box indicates that an error will be generated if such a connection is found.

Our circuit contains only Passive Pins (on resistors, capacitors and the connector) and Input Pins (on the transistors. Let's check to see if the connection matrix will detect unconnected passive pins.

Look down the row labels to find Passive Pin. Look across the column labels to find Unconnected. The square where these entries intersect indicates the error condition when a Passive Pin is found to be Unconnected in the

schematic. The default is a green square, which indicates that no report will be generated.

Click on this intersection box until it turns yellow so that a warning will be generated for unconnected passive pins when we compile the project. We will purposely create an instance of this error to check it later in this tutorial.

### Setting up the Comparator

The **Comparator** tab in the *Options for Project* dialog sets which differences between files will be reported or ignored when a project is compiled. For this tutorial, we do not need to show differences between some features that refer to hierarchical schematic designs only, such as rooms. Make sure you do not accidentally ignore components when you meant to ignore component classes!

- 1. Click on the **Comparator** tab and find **Changed Room Definitions**, **Extra Room Definitions** and **Extra Component Classes** in the Difference Associated with Components section.

- Select Ignore Differences from the drop-down list in the Mode column to the right of the these options.

| Options for PCB | Project Multivi            | brator.PrjPCB    |               |                      |            |               |                  |                   | ? 🗙        |

|-----------------|----------------------------|------------------|---------------|----------------------|------------|---------------|------------------|-------------------|------------|

| Error Reporting | Connection Matrix          | Class Generation | Comparator    | ECO Generation       | Options    | Multi-Channel | Default Prints   | Search Paths      | Parameters |

| Comparison Type | Description                |                  |               |                      |            | ∆ Mo          | ode              |                   | ~          |

|                 | sociated with Comp         | onents           |               |                      |            |               |                  |                   |            |

|                 | hannel Class Name          |                  |               |                      |            |               | Find Differences |                   |            |

|                 | omponent Class Na          | me               |               |                      |            |               | Find Differences |                   |            |

|                 | et Class Name              |                  |               |                      |            |               | Find Differences |                   |            |

|                 | oom Definitions            |                  |               |                      |            |               | Find Differences |                   | <b>_</b>   |

| Changed R       | ule<br>asses With Extra Me |                  |               |                      |            |               | Ignore Differenc |                   |            |

|                 | Classes With Extra Me      |                  |               |                      |            |               | Find Differences | •                 |            |

| Different Co    |                            | Members          |               |                      |            |               | Find Differences |                   |            |

| Different De    |                            |                  |               |                      |            |               | Find Differences |                   |            |

| Different Fo    |                            |                  |               |                      |            |               | Find Differences |                   |            |

| Different Lib   | orary References           |                  |               |                      |            |               | Find Differences |                   |            |

| Different Ty    |                            |                  |               |                      |            |               | Find Differences |                   |            |

| Extra Chann     |                            |                  |               |                      |            |               | Find Differences |                   |            |

|                 | onent Classes              |                  |               |                      |            |               | Find Differences |                   |            |

| Extra Comp      |                            |                  |               |                      |            |               | Find Differences |                   |            |

| Extra Room      |                            |                  |               |                      |            |               | Find Differences |                   | ~          |

|                 | accusted with filete       |                  |               |                      |            |               |                  |                   |            |

|                 |                            |                  |               | Object Matching Crit |            |               |                  |                   |            |

| Object Type     | Min Match                  |                  | atched Member |                      | me Matchir | -             |                  | al Matching Dialo | g          |

| Net             | 75                         | 3                |               |                      | member m   |               |                  | tched objects     |            |

| Net Class       | 75                         | 3                |               |                      | member m   | -             | -                | tched objects     |            |

| Component Class | 75                         | 3                |               | 🍼 After              | member m   | natching      | 🌏 For unma       | tched objects     |            |

|                 |                            |                  |               |                      |            |               |                  |                   |            |

|                 |                            |                  |               |                      |            |               |                  |                   |            |

| Ignore Rules    | s Defined in PCB Or        | ıly              |               |                      |            |               |                  |                   |            |

| Set To Default  |                            |                  |               |                      |            |               |                  | ПК                | Cancel     |

|                 | <u> </u>                   |                  |               |                      |            |               |                  |                   | Cancer     |

Now we are ready to compile the project and check for any errors.

# **Compiling the project**

Compiling a project checks for drafting and electrical rules errors in the design documents and puts you into a debugging environment. We have already set up the rules in the Error Checking and Connection Matrix tabs of the *Options for Project* dialog.

- 1. To compile our Multivibrator project, select Project » Compile PCB Project.

- 2. When the project is compiled, any errors generated will display in the Messages panel. Click on this panel to check for errors (View » Workspace Panels » System » Messages). The compiled documents will be listed in the Navigator panel, together with a flattened hierarchy, components and nets listed and a connection model that can be browsed.

If your circuit is drawn correctly, the Messages panel should not contain any errors. If the report gives errors, check your circuit and ensure all wiring and connections are correct.

We will now deliberately introduce an error into our circuit and recompile the project:

- 1. Click on the Multivibrator.SchDoc tab at the top of the design window to make the schematic sheet the active document.

- 2. Click in the middle of the wire that connects R1 to the base wire of Q1. Small, square editing handles will appear at each end of the wire and the selection color will display as a dotted line along the wire to indicate that it is selected. Press the **DELETE** key to delete the wire.

- Recompile the project (Project » Compile PCB Project) to check that any errors are found. The Messages panel will display warning messages indicating you have unconnected pins in your circuit. Select View » Workspace Panels » System » Messages if the Messages panel is not displayed.

- 4. Double-click on an error or warning in the Messages panel and the *Compile Error* window will display with details of the violation. From this window, you can click on an error and jump to the violating object in a schematic to check or correct the error.

Before we finish this section of the tutorial, let's fix the error in our schematic.

- 1. Click on the tab of the schematic sheet to make it active.

- Select Edit » Undo from the menus [shortcut Ctrl+Z]. The wire you deleted previously should now be restored.

- To check that the undo was successful, recompile the project (Project » Compile PCB Project) to check that no errors are found. The Messages panel should show no errors.

If you wish to clear messages from the Messages panel, rightclick in the window and select **Clear All**.

- Select View » Fit All Objects [shortcut V, F] from the menus to restore your schematic view and save your error-free schematic.

- 5. Save the schematic and the project file as well.

Now we have completed and checked our schematic, it is time to create the PCB.

# **Creating a new PCB document**

Before you transfer the design from the Schematic Editor to the PCB Editor, you need to create the blank PCB with at least a board outline. The easiest way to create a new PCB design in Altium Designer is to use the PCB Wizard, which allows you to choose from industry-standard board outlines as well as create your own custom board sizes. At any stage you can use the **Back** button to check or modify previous pages in the wizard.

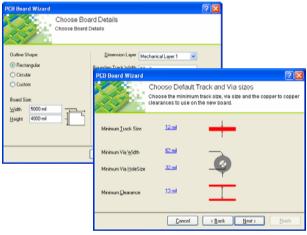

To create a new PCB using the PCB Wizard, complete the following steps:

- Create a new PCB by clicking on PCB Board Wizard in the New from Template section at the bottom of the Files panel. If this option is not displayed on the screen, close some of the sections above by clicking on the up arrow icons.

- 2. The PCB Board Wizard opens. The first screen you see is the introduction page. Click the **Next** button to continue.

- Set the measure units to Imperial, i.e. 1000 mils = one inch.

- The third page of the wizard allows you to select the board outline you wish to use. For this tutorial we will enter our own board size. Select Custom from the list of board outlines and click Next.

- In the next page you enter custom board options. For the tutorial circuit, a 2 x 2 inch board will give us plenty of room. Select **Rectangular** and type 2000 in both the Width and Height fields. Deselect **Title Block & Scale**,

Legend String and Dimension Lines. Click Next to continue.

- 6. This page allows you to select the number of layers in the board. We will need two signal layers and no power planes. Click **Next** to continue.

- 7. Choose the via styles used in the design by selecting Thruhole Vias only and click Next.

- The next page allows you to set the component/track technology (routing) options. Select the Through-hole components option and set the number of tracks between adjacent pads to One Track. Click Next.

- 9. The next page, *Default Track and Via Sizes*, allows you to set up some of the design rules that apply to your board. Leave the options on this screen set to their defaults. Click the **Next** button to continue.

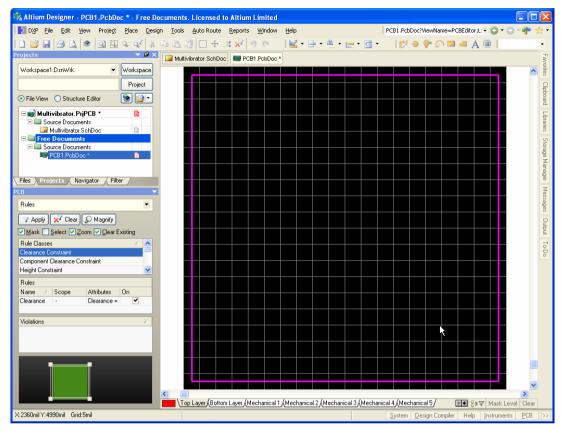

- 10. Click **Finish** to close the Wizard. The PCB Wizard has now collected all the information it needs to create your new board. The PCB Editor will now display a new PCB file named PCB1.PcbDoc.

11. The PCB document displays with a default sized white sheet and a blank board shape (black area with grid). To turn it off, select **Design** » **Board Options** and deselect **Display Sheet** in the *Board Options* dialog.

For more tutorials, press **F1** to access the Altium Designer Documentation Library.

You can add your own border, grid reference and title block from other PCB templates supplied with Altium Designer.

- For more information about using board shapes, sheets and templates, refer to the *Preparing the Board for Design Transfer* tutorial.

- 12. Now the sheet has been turned off, display the board shape only by selecting **View** » **Fit Board** [shortcut **V**, **F**].

- 13. The PCB document is automatically added (linked) to the project and is listed under Source Documents beneath the project name in the **Projects** tab. Rename the new PCB file (with a .PcbDoc extension) by selecting **File** » **Save As**. Navigate to a location where you would like to store the PCB on your hard disk, type the name Multivibrator.PcbDoc in the File Name field and click on **Save**.

#### Adding a new PCB to a project

If the PCB you want to add to a project file has been opened as a Free Document, right-click on the PCB project file in the Projects panel and select **Add Existing to Project**. Choose the new PCB file

name and click on **Open**. The PCB is now listed under Source Documents beneath the project in the **Projects** panel and is linked to the project file. Save the project file.

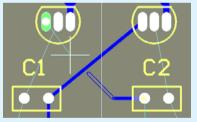

## Transferring the design

Before transferring the schematic information to the new blank PCB, make sure all the related libraries for both schematic and PCB are available. Since only the default installed integrated libraries are used in this tutorial, the footprints will already be included. Once the project has been compiled and any errors in the schematic fixed, use the **Update PCB** command to generate ECOs that will transfer the schematic information to the target PCB.

### **Updating the PCB**

To send the schematic information to the target PCB in your project:

- 1. Open the schematic document, Multivibrator.SchDoc.

- 2. Select **Design** » **Update PCB Document** (Multivibrator.PcbDoc). The project compiles and the *Engineering Change Order* dialog displays.

| Er | gineering      | g Change Order    |                             |        |                   |        |      | ? 🗙     |

|----|----------------|-------------------|-----------------------------|--------|-------------------|--------|------|---------|

| Mo | odifications   |                   |                             |        |                   | Status |      |         |

|    | Enable $ able$ | Action            | Affected Object             |        | Affected Document | Check  | Done | Message |

| Ξ  |                | Add Components(9) |                             |        |                   |        |      |         |

|    | ✓              | Add               | 📕 C1                        | To     | H H               |        |      |         |

|    | ✓              | Add               | 📕 C2                        | То     | 開始                |        |      |         |

|    | ✓              | Add               | 🌗 Q1                        | То     |                   |        |      |         |

|    | ✓              | Add               | 🕕 Q2                        | То     |                   |        |      |         |

|    | ✓              | Add               | 🕕 R1                        | То     | 調整                |        |      |         |

|    | ✓              | Add               | 📙 R2                        | То     | HEP               |        |      |         |

|    | ✓              | Add               | 🕕 R3                        | То     |                   |        |      |         |

|    | ✓              | Add               | 📕 R4                        | То     |                   |        |      |         |

|    | ✓              | Add               | 🕕 Y1                        | То     | HB)               |        |      |         |

| Ξ  |                | Add Nets(6)       |                             |        |                   |        |      |         |

|    | ✓              | Add               | 🔁 12V                       | То     |                   |        |      |         |

|    | ✓              | Add               | 🔁 GND                       | То     | 開設                |        |      |         |

|    | ✓              | Add               | ≈ NetC1_1                   | То     | H H               |        |      |         |

|    | ✓              | Add               | 🔁 NetC1_2                   | To     | HP.               |        |      |         |

|    | ✓              | Add               | ≈ NetC2_1                   | To     | H H               |        |      |         |

|    | ✓              | Add               | 🔁 NetC2_2                   | То     | 開始                |        |      |         |

|    |                |                   |                             |        |                   |        |      |         |

|    | /alidate Cha   | nges Execute Cha  | nges <u>R</u> eport Changes | 🗌 Only | Show Errors       |        |      | Close   |

- Click on Validate Changes. If all changes are validated, the green ticks appear in the Status list. If the changes are not validated, close the dialog, check the Messages panel and clear any errors.

- 4. Click on **Execute Changes** to send the changes to the PCB. When completed, the Status changes to Done.

You can create a report of ECOs to print out by clicking on the **Report Changes** button.

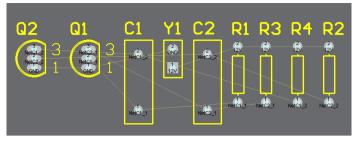

Click Close and the target PCB opens with components positioned ready for placing on the board. Use the shortcut keys V, D (View Document) if you cannot see the components in your current view.

Figure 4. The components next to the board, ready for positioning.

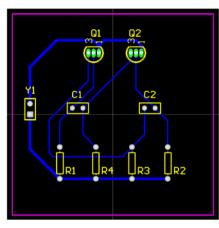

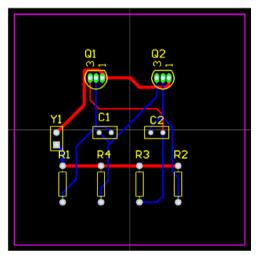

# **Designing the PCB**

Now we can start placing the components on the PCB and routing the board.

### Setting up the PCB workspace

Before we start positioning the components on the board, we need to set up the PCB workspace, such as the grids, layers and design rules.

#### Grids

We need to ensure that our placement grid is set correctly before we start positioning the components. All the objects placed in the PCB workspace are aligned on a grid called the *snap grid*. This grid needs to be set to suit the routing technology that you intend to use.

Our tutorial circuit uses standard imperial components that have a minimum pin pitch of 100mil. We will set the snap grid to an even fraction of this, say 50 or 25mil, so that all

component pins will fall on a grid point when placed. Also, the track width and clearance for our board are 12mil and 13mil respectively (the default values used by the PCB Board Wizard), allowing a minimum of 25mil between parallel track centers. The most suitable snap grid setting would, therefore, be 25mil.

To set the snap grid, complete the following steps:

- 1. Select **Design** » **Board Options** [shortcut **D**, **O**] to open the *Board Options* dialog.

- Set the values of the Snap Grid and the Component Grid to 25mil using the drop-down lists or typing in the value. Note that this dialog is also used to define the Electrical Grid. The Electrical Grid operates when you place an electrical object; it overrides the snap grid and snaps electrical objects together. Click OK to close the dialog.

Let's set some other options that will make positioning components easier.

Select Tools » Preferences [shortcut T, P] to open the Preferences dialog. Click on PCB Editor – General in the dialog's selection tree (left side panel) to display the PCB Editor – General page. In the Editing Options section, make sure the Snap to Center option is checked. This ensures that when you "grab" a component to position it, the cursor is set to the component's reference point.

| + 📴 System<br>€ 🛅 Schematic<br>+ 🛅 FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PCB Editor – Ge | neral                                                                                                                                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Wersion Control</li> <li>Wersion Control</li> <li>Embedded System</li> <li>PCB Editor</li> <li>PCF Editor</li> <li>PCB 20</li> <li>PCB 20</li> <li>Text Editors</li> <li>PCA Editor</li> <li>PCB AD</li> <li>PCB</li></ul> | Editing Options | Autopan Options Style Adaptive Speed 1200 Pixels/Sec Mils/Sec Polygon Repour Repour Repour Threshold 5000 Elle Format Change Repot Disable opening the report from older versions Disable opening the repot from newer versions |

Click on PCB Editor – Board Insight Display in the *Preferences* dialog's selection tree to make it the active page. In the Pad and Via Display Options section of this page, uncheck the Pad Nets, Pad Numbers and Via Nets options. Lastly, click on PCB Editor – Display. In the Draft Thresholds section of this page, check the Strings field is 4 pixels and click OK to close the Display of the Pad Nets.

| Preferences dialog.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                  |             |                                                    |                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------|----------------------------------------------------|----------------|

| Preferences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                  |             |                                                    | ? 🛛            |

| System     System     Schematic     Fr6A     Wersion Control     Embedded System     PCB Editor     General     Display     Board Insight Modes     Board Insight Modes     Board Insight Hodes     Board Insight Modes     Board Insight Modes | PCB Edit         | tor – Board | Net Names of<br>Display<br>Single Layer<br>Current |                |

| Set To Defaults 🔻 Save                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Load Import From | •           | 0                                                  | K Cancel Apply |

### Defining the layer stack and other non-electrical layers

If you look at the bottom of the PCB workspace, you will notice a series of layer tabs. The PCB Editor is a multi-layered environment and most of the editing actions you perform will be on a particular layer. Select **Design** » **Board Layers & Colors** [shortcut **L**] to display the *Board Layers & Colors* dialog where you can display, add, remove and rename and set the colors of the layers.

| loard Layers and                               | Colors        |                 |                     |             |      |                         |          |          |           |                         | ?                  |

|------------------------------------------------|---------------|-----------------|---------------------|-------------|------|-------------------------|----------|----------|-----------|-------------------------|--------------------|

| Signal Layers (S)<br>Top Layer<br>Bottom Layer | Color         | Show            | Internal Planes (P) | Color       | Show | Mechanical<br>Layers(M) | Color    | Show     |           | Single<br>Layer<br>Mode | Linked To<br>Sheet |